FPGA

AIT鉄人1号ではSH7045Fで時分割のPWM信号を発生し、CPLDで各サーボに信号を振り分けていた。AIT鉄人2号では、まずCPUをより高速なSH7145Fに変更し、さらにPWM信号の生成をFPGAに行わせるようにした。また、センサ信号もFPGAで処理させた。FPGAとはField

Programmable Gate Arrayの略で、プログラミングできるLSIを言う。CPLDもFPGAと同じようにプログラミングできるLSIだが、規模が小さくて、PWM信号を1個のCPLDで発生させることができなかったが、FPGAによりそれらが可能になった。このように信号処理を専用LSに任せることにより、CPUの負荷を減らし、高精度、高速な処理ができるようになる(かな?)。また、通常行われているようなトリッキーなプログラムが不要に成り、制御プログラミングも簡単でわかりやすく成る。FPGAはSH7145FのCS2のメモリー空間にマッピングし、マッピングされたアドレスへPWMの値をWRITEするだけで、PWM信号が出力される。また、角速度ジャイロセンサーのパルス幅もFPGAで計測し、マッピングされたアドレスからREADするだけで、センサー信号を読み込むことができる。SH7145Fは16ビットデータバス、8ビットアドレスバスでFPGAと接続している。

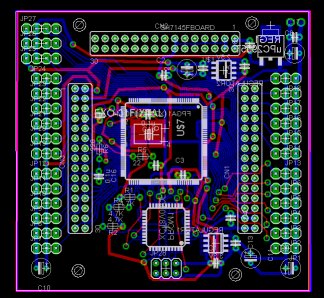

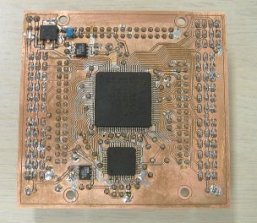

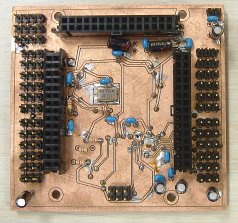

今回のボードは、FPGAとコンフィグレーションPROMだけのシンプルなもの。回路図をEagleで書き、自動配線でパターンをある程度生成(実際には自動ではほとんどパターンはできません)した後、人力でパターン修正。データを基板加工機で読み込んで基板製作した。表面実装です。ボードの主な構成は以下のよう。これだけの機能を入れてもFPGAのゲートは1/3も使われていない。今後は、さらに機能を入れていく予定。

| FPGA | XILINX SPARTAN II (XC2S100TQ144) 10万ゲート User I/O 92 |

| コンフィグレーションEEPROM | XC18V01VQ44 1Mbit |

| 開発ツール | Xilinx社WebPACK ISE |

| 回路設計、パターンレイアウト | Eagle4.11 |

| CAM | CAM-21RS |

| プリント基板自動加工機 | FP-7A(MITS) |

| 使用基板 | 両面基板 表面実装 |

| 出力 | PWM×24(サーボ用:分解能0.5µs、周期16.384ms、パルス幅0-8,192ms) PWM×3 (角速度ジャイロセンサ用:周期16.384ms、パルス幅1.024ms固定) |

| 入力 | パルス幅×3(角速度ジャイロセンサ用:分解能0.5µs、計測パルス幅0-8.192ms) |

|

| SH7145Fボードのメモリマップ FPGAとは、CS2空間で8ビットアドレスで接続 |

|

| 回路の全体構成 |

|

|

| PWMユニット | ジャイロセンサユニット |

|

|

| VHDLでFPGAの回路を記述 |

|

|

| Eagleで回路設計、基板パターン作成 | |

|

|

|

| 基板加工機で基板製作 | 部品を半田付けして完成(裏面/表面) | |

|

| SH7145F(ベストテクノロジーBTC080) ボードと合体 |